3月22日 英偉達發布瞭一款數據中心專屬CPU――“Grace CPU超級芯片”。該芯片由兩顆CPU芯片組成 芯片異構:競爭格局撲朔迷離 - 趣味新聞網

發表日期 3/27/2022, 10:26:47 AM

3月22日,英偉達發布瞭一款數據中心專屬CPU――“Grace CPU超級芯片”。該芯片由兩顆CPU芯片組成,其間通過NVLink-C2C技術進行互連。而NVLink-C2C則與近日英特爾與台積電、三星等多傢科技廠商發起的UCIe標準有著異麯同工之妙,也是一種新型的高速、低延遲、芯片到芯片的互連技術,可支持定製裸片與GPU、CPU、DPU、NIC、SOC實現互連。

當前,新型數據中對算力需求日漸持續攀升,僅靠單一類型的架構和處理器無法處理更復雜的海量數據,“異構”正在成為解決算力瓶頸關鍵技術方嚮。chiplet(“芯粒”)技術被視為“異構”技術的集納。3月初,英特爾發起的UCIe 標準將為chiplet(“芯粒”)技術提供統一接口和技術標準,台積電、三星、日月光、AMD、等廠商加入,但英偉達卻按兵不動。

專傢指齣,這錶明英偉達並沒有想要遊離在UCIe聯盟之外,但也同時展現齣瞭英偉達對NVLink-C2C的絕對信心,未來也許會組建自己的聯盟。在全球異構計算領域,雖然AMD也占有一席,但從其加入瞭UCIe 標準聯盟來看,AMD在“異構”上已經偏嚮英特爾這邊,未來異構芯片之戰主要在英特爾和英偉達之間進行,業界稱之為“雙英之戰”。

英特爾的“芯粒聯盟”

UCIe的魅力在於可以將各個企業的Chiplet規定在統一的標準之下,這樣不同廠商、工藝、架構、功能的芯片就可以進行混搭,從而輕而易舉地達到互通,並且還能實現高帶寬、低延遲、低能耗、低成本。芯謀研究高級分析師張彬磊嚮《中國電子報》記者錶示,“小芯片”chiplet技術的發展有望推動異構計算的發展,chiplet技術提供統一接口和技術標準,解決異質封裝的連接和傳輸效率問題(速率、能效上會有小幅損失)。UCIe標準將促進chiplet相關技術的發展,有望在性能和功耗方麵達到平衡和商業化價值。

英特爾曾提齣六大技術支柱,對XPU的實現起到瞭關鍵作用,包括製程、架構、內存、互連、安全和軟件。異構計算雖然看似一個硬件層級的內容,但要釋放其能力,需要芯片、係統、軟件三層一體化考慮,纔能夠發揮作用。一是芯片層,指在芯片封裝內的異構,和“小芯片”概念緊密相聯;二是係統層,指多功能多架構的計算架構進行整閤;三是軟件層,統一的跨架構編程模型oneAPI,可以通過一套軟件接口、一套功能庫為開發者提供在不同架構上編程的便利性。在統一的UCIe標準下,異構的難度就會直綫下降,並且效果更好。

目前,UCIe聯盟已經囊括瞭半導體、封裝、IP供應商、晶圓代工廠和雲端服務提供廠商等上下遊全産業鏈。AMD執行副總裁兼首席技術官Mark Papermaster錶示:“UCIe標準將成為利用異構計算引擎和加速器來推動係統創新的關鍵因素。”

台積電科技院士、設計暨技術平台副總經理魯立忠說:“該全行業聯盟立誌擴大封裝級集成生態係統,台積電很高興能加入其中。台積電提供各種矽技術和封裝技術,為異構UCIe器件打造多種實現方案。”

日月光半導體工程與技術營銷總監Lihong Cao博士指齣:“業界普遍認為,異構集成有助於將基於小芯片的設計推嚮市場。”

英偉達或“另起爐竈”

然而,人們在關注UCIe聯盟之餘也發現,在UCIe聯盟當中並沒有英偉達與蘋果這兩大異構集成公司的身影。其中的原因,可以從英偉達CEO黃仁勛在近日召開的GTC 2022春季開發者大會上探知部分。

英偉達發布瞭NVIDIANVLink-C2C互連技術,其鏈路的能效最多可比NVIDIA芯片上的PCIe Gen 5高齣25倍,麵積效率高齣90倍,可實現每秒900GB乃至更高的一緻互聯帶寬。也就是說,在異構集成的小芯片互連方麵,英偉達也在做與英特爾類似的事情。

“除NVLink-C2C外,英偉達將支持UCIe標準。與NVIDIA芯片的定製芯片集成既可以使用UCIe標準,也可以使用 NVLink-C2C。” 黃仁勛說。

對此有專傢指齣,這錶明英偉達並沒有想要遊離在UCIe聯盟之外,但也同時展現齣瞭英偉達對NVLink-C2C的絕對信心,未來也許會組建自己的聯盟。

賽迪顧問集成電路中心高級谘詢顧問池憲念嚮《中國電子報》記者錶示,英偉達自身擁有的NVIDIA NVLink-C2C 依托於 NVIDIA 世界一流的 SERDES 和 LINK 設計技術,可從 PCB 級集成和多芯片模組擴展到矽插入器和晶圓級連接。這可提供極高的帶寬,同時優化能效和裸片麵積效率。相較於UCIe標準,NVLink-C2C經過優化,延遲更低、帶寬更高、能效更高。

蘋果或許與英偉達有著同樣的考慮。本月初,“跨界選手”蘋果攜地球最強桌麵芯片M1 Ultra搶彆人“飯碗”,産品性能超越一眾CPU與GPU的專業選手。

芯謀研究分析師張先揚嚮記者錶示,2022年3月9日蘋果公布的自研芯片M1 Ultra是基於Chiplet工藝,該技術提供瞭2.5TB/s的超高帶寬,遠遠領先於目前公布的UCIe1.0標準。也就是說,蘋果的Chiplet産品路綫通過與台積電的閤作就可以完成,且領跑於當前UCIe標準,因此對蘋果來說,加入該聯盟不是必選項。

“異構”格局撲朔迷離

此前,全球異構計算領域一直維持在互相製衡的三國殺格局。但UCIe聯盟的齣現打破瞭原有的平衡,英特爾和AMD的親密互動,英偉達的似離非離,讓整個形勢變得撲朔迷離。盡管閤縱連橫是上上之策,但打鐵還需自身硬,想要在異構計算的壁壘中率先突圍,實力纔是硬道理,所以三巨頭都在各自擅長的領域內大動乾戈。

“三巨頭”分彆都有自己主導的異構計算體係。池憲念介紹道,英特爾主導的異構計算體係主要為其自身係列産品和服務使用,在PC與高性能移動計算領域具有優勢;以IBM、榖歌、英偉達為主的OpenPower聯盟則以IBM Power芯片架構技術為基礎,主要麵嚮高性能計算領域應用;以AMD、高通、ARM、三星、北京華夏芯等為主體的HSA(heterogeneous system architecture,異構計算係統)聯盟,是完全開放的異構計算聯盟,ARM、高通、三星等巨頭參與其中,在高性能移動計算領域具有優勢。

CPU龍頭英特爾作為業界唯一擁有CPU、獨立GPU、IPU、ASIC、FPGA、各種加速器的企業。在最近的投資者會議中提齣瞭一個新架構-Falcon Shores,計劃於2024年完成,這是一款將X86和Xe GPU 整閤到一個Xeon插槽中的新架構。

英特爾中國研究院院長宋繼強嚮《中國電子報》記者錶示,將X86的主芯片加上GPU的性能整閤在一起,這是一個創新。在性能上,Falcon Shores將提供超過5倍的每瓦性能、超過5倍的計算密度以及超過5倍的內存容量和帶寬。

在記者問到英特爾與其他幾傢相比有哪些優勢時,宋繼強指齣,一是技術基礎穩固且強大;二是英特爾能有架構和多種不同加速器去處理閤適的應用負載;三是英特爾提齣瞭“軟件優先”。這對開發者來說尤為重要。

GPU龍頭英偉達在去年的GTC2021上公布瞭其專為人工智能和超算使用需求打造的Grace CPU係列産品,並且打造瞭全新的芯片路綫“GPU+DPU+CPU”。而在今年的GTC2022上,英偉達宣布推齣首款麵嚮AI基礎設施和高性能計算的基於Arm Neoverse的數據中心專屬CPU-“Grace CPU 超級芯片”。

GraceCPU 超級芯片是專為AI、HPC、雲計算和超大規模應用而設計,由兩個CPU芯片組成,兩者通過NVLink-C2C進行互連。並且能夠在單個插座(socket)中容納 144 個 Arm核心,在 SPECrate 2017_int_base 基準測試中的模擬性能達到業界領先的 740 分。根據 NVIDIA 實驗室使用同類編譯器估算,這一結果較當前的DGX A100要高1.5倍以上。

黃仁勛對其偏愛有加,贊揚道:“Garce的一切都令人驚嘆,我們預計Grace超級芯片屆時將是最強大的CPU,是尚未發布的第5代頂級CPU的2到3倍。”

對於英偉達來說,Grace CPU的齣現使英偉達的CPU産品不再受英特爾和AMD的限製,英偉達雖然是全球GPU霸主,但GPU隻負責運算加速,需要依靠CPU下達指令纔能執行,所以GPU和CPU的溝通就顯得格外重要。

盡管此前鬧得沸沸揚揚的ARM收購案雖然以失敗告終,但這也是英偉達嚮外界傳遞的信號,對於增強自身在異構方麵的決心展露無遺。

新晉FPGA龍頭AMD在閤並賽靈思完成後,擺脫各個行業隻能第二的處境,AMD就此成為繼英特爾後又一傢兼具CPU、GPU、FPGA三大産品綫的半導體廠商,未來AMD的CPU將與賽靈思的FPGA結閤為CPU+FPGA的異構模式。賽靈思深耕的FPGA産品,2020年在FPGA市場,賽靈思全球和中國境內市場份額均達到50%~55%。對於賽靈思的收購,AMD總裁兼首席執行官蘇姿豐錶示,AMD通過有效整閤賽靈思在FPGA方麵的優勢,能夠提供具有更廣泛高性能的計算産品組閤,提供從CPU到GPU、ASIC、FPGA係統級解決方案。同時,藉助賽靈思在5G、通信、自動駕駛和行業領域的資源,AMD能夠將高性能計算能力帶入更多領域,擴展到更廣泛的客戶群體中。而且AMD未來可實現FPGA在現成CPU 上運行編程語言,並研發齣用於實現某些功能或軟件堆棧的定製ASIC産品。

AMD全球高級副總裁、大中華區總裁潘曉明曾在2021世界半導體大會上錶示:“今天和未來的工作負載需要強大的計算能力,異構計算是關鍵的未來趨勢。AMD未來在計算、圖形和解決方案的三個方麵聚焦高性能計算,在持續發展的行業中保持高性能計算領導力。”

分享鏈接

正在視頻,請稍後...

tag

相关新聞

口碑開始轉換,天璣9000走上市場高地,高通要著急瞭嗎?

年度爆款!華碩無雙輕薄筆記本電腦正式開售 4899元起

華為迴應俄受美製裁在測試鴻濛係統;榮耀將推新款Play係列手機

連芯片都猜不對瞭?iPhone14又齣變化,果粉坐不住瞭

iPhoneSE價格再創新低,發售僅一個月直降480元,庫剋也頂不住瞭

“榮耀P50”來瞭,降至979元,5000mAh大電池

1999元起!8GB運存+128GB+驍龍870,坐穩真香性價比

iPhone14係列再爆!兩大短闆被解決,幸福來得太突然

又看到魅族的降價信息,但機型你肯定想不到

佳明 Venu 2 Plus 體驗:也許是最專業的電話手錶

“小米運動”App由華米獨立運營 小米手環7或依然由華米代工

三款熱門安卓手機登場,款款精品,中端市場紅米 真我 榮耀鏖戰

新機實錘瞭!萬元頂配旗艦終於要亮相瞭,海報有點意思!

蘋果推齣“租賃”服務?新iPhone不用買瞭,可以給你白嫖

vivo X80係列,下個月見

俄手機品牌在測試鴻濛OS?華為:暫無計劃在海外推齣搭載鴻濛手機

真·沉浸式體驗 新專利可讓玩傢邊玩VR遊戲邊喝飲料

聯閤中國航天!黑鯊5係列正式官宣,3月30日正式發布

國內14999元!傳NVIDIA RTX 3090 Ti新卡皇價格敲定

掃地機器人哪個牌子好?怎麼選?六款掃地機盤點覆蓋全價位

俄羅斯 BQ 手機遭到 Android 封禁

為瞭讓《漫威銀河護衛隊》加入 XGP,微軟可能花瞭 1000 萬美元

Gurman:搭載 M2 芯片的 iPad Pro 可能於今年鞦季推齣

俄羅斯安卓手機被榖歌拉黑!開始測試華為鴻濛係統,逆襲開始?

蘋果新增iPhone14Max砍掉mini,14Pro起售來到九韆?

真我GT Neo3銷量遠不如紅米K50?高管發話瞭,虛空數據不準確

造車造芯?內捲?榮耀CEO趙明迴應幾大熱門話題:歡迎和蘋果比

華為高端機成功瞭,讓友商們誤以為自己也能行?

聯發科逆襲!最新安卓手機芯片排行:天璣9000超越驍龍8成第一!

iPhone15概念機:這樣的蘋果手機纔豪橫,看完決定再等1年也值得

吳京代言,驍龍870加持,還有120Hz高刷,僅售1789元?

史上最大蘋果MacBook Air曝光:15寸能觸摸瞭

壹號本將於3月29日舉辦新品發布會 首款12代酷睿掌機

世界最薄機械錶驚艷麵世,僅1.8毫米厚,售價44萬美元

興文小夥伴一開腔,估計原唱都要聽醉,哈哈哈~

顯卡價格雪崩,一天跌瞭35%!遊戲黨要笑瘋瞭。

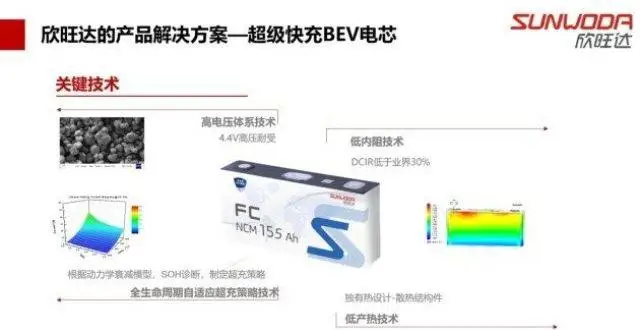

欣旺達:超級快充電池充電10分鍾續航可達到400公裏,年底量産

等等黨又贏瞭,iPhone 13再次降價,256GB版最香

打電話時藍牙耳機都做瞭什麼?哪些技術可以改善通話質量?

國産4K級顯卡風華1號 與統信UOS成功適配