資料來源:物聯傳媒(ulinkmedia)作者:麥穗、銀匠物聯網智庫 轉載導讀在3月2日 ASE、AMD、ARM、Google雲、Intel、Meta(Facebook)、微軟、高通、三星、台積…… Chiple小芯片迎來統一標準,終結IoT碎片化之痛? - 趣味新聞網

發表日期 3/5/2022, 5:00:09 PM

資料來源: 物聯傳媒(ulinkmedia)

作者: 麥穗、銀匠

物聯網智庫 轉載

導讀

在3月2日,ASE、AMD、ARM、Google雲、Intel、Meta(Facebook)、微軟、高通、三星、台積電十大行業巨頭聯閤宣布,成立行業聯盟,共同打造小芯片互連標準、推進開放生態,並製定瞭標準規範“UCIe”。

Chiplet“小芯片”在2019年小火過一把,當時Chiplet在AI芯片領域可謂熱詞,但在更早之前這個概念就已經齣現瞭。 Chiplet是矽片級彆的重用 ,是一類滿足特定功能的die,通過搭積木造芯片的模式,利用die-to-die內部互聯技術將多個模塊芯片與底層基礎芯片封裝在一起,構成多功能的異構System in Packages(SiPs)芯片的模式,建立一個Chiplet的芯片網絡。

這也被認為是能延續摩爾定律“已死”的重要方案。

2019年AMD提齣打破摩爾定律的限製,革命性的the Infinity Fabric(兩個4核CPU互聯的專門的通道)掀起瞭小芯片風潮。那時候對於這項技術的限製大部分都會提到 互聯 標準 和 封裝技術 。

在3月2日,ASE、AMD、ARM、Google雲、Intel、Meta(Facebook)、微軟、高通、三星、台積電十大行業巨頭聯閤宣布,成立行業聯盟,共同打造小芯片互連標準、推進開放生態,並製定瞭標準規範“UCIe”。

UCIe標準的全稱為“Universal Chiplet Interconnect Express”(通用小芯片互連通道), 在芯片封裝層麵確立互聯互通的統一標準,可在小芯片之間提供高帶寬、低延遲、節能且具有成本效益的封裝連接。

UCIe 1.0標準定義瞭芯片間I/O物理層、芯片間協議、軟件堆棧等,並利用瞭PCIe、CXL兩種成熟的高速互連標準。這個標準最初是由Intel提齣並製定,後開放給業界,共同製定而成。

它解決瞭對計算、內存、存儲和跨越雲、邊緣、企業、5G、汽 、 性能計算和 持領域的整個計算連續體的連接。 UCIe 提供瞭封裝來自不同來源的芯 的能力,包括不同的晶圓廠,不同的設計和不同的封裝技術。這一波直接衝擊的是芯片半導體行業,但其覆蓋的垂直領域市場也是不可計量的。

為何是Chiplet封裝集成?

我們先來區分一下SOC、SIP和Chiplet。

SOC(system on chip)片上係統。 它是信息係統核心的芯片集成,是將係統關鍵部件集成在一塊芯片上,像一個微小型係統。在PC時代我們可以說一個電腦的核心是CPU,而在智能終端時代,手機的核心就是SOC。它依然是遵循摩爾定律發展方嚮的。

SOC模擬示意圖,圖源網絡

SIP(System-in Package)係統級封裝。 SIP封裝並無一定型態,利用單純的打綫結閤或覆晶接閤,將處理器、存儲器、FPGA等功能芯片以2D或者3D封裝結構集成在一個封裝內,可做定製化生産。SIP超越瞭摩爾定律的發展方嚮,在SIP中集成度較高的是藍牙和802.11(b/g/a),多用於涵蓋通信技術的解決方案,同時UWB是SIP的另一個理想應用。

Chiplet即芯粒,也稱小芯片。 它其實就是多個芯粒通過先進的封裝技術形成的SIP,將不同工藝節點和不同材質的芯片通過先進的集成技術(如3D集成技術)封裝集成在一起,形成一個係統芯片,實現瞭一種新形式的IP復用。它擺脫瞭摩爾定律的發展方嚮。

UCIe 支持在封裝上交付平台的開放式 Chiplet 態係統

發展瞭50多年的摩爾定律已然快到極限,現在行業的需求對於傳統單一工藝、單一芯片的做法來說,難度和成本都越來越高,亟需變革。 芯 的封裝集成能夠以快速且經濟 效的 式提供定製解決 案,例如,不同的 途可能需要 同的加速能力,但具有相同的內核、內存和 I/O。現在,它還允許根據功能進行最佳工藝節點選擇的芯 共同封裝,通過UCIe實現小芯片之間的封裝互連,可以大大降低製造成本。

數據顯示, 10nm芯片的設計成本為1.744億美元,7nm芯片飆升到2.978億美元,5nm芯片更是高達5.422億美元 ,即便是行業巨頭也越來越吃力。而新的UCIe標準規範,讓不同廠商的小芯片互通成為可能,x86、ARM、RISC-V集成在一起也有瞭實現之地。

UCIe 1.0 定義瞭兩種類型的封裝: 物理層 和 通信 協議 。 先是封裝級集成,連接在闆級的組件,如內存、加速器、網絡設備、調製解調器等,可以在封裝級集成,適 於從 持到 端服務器,通過 同的封裝選項連接來 多個來源的芯 。其次是使 不同類型的介質(例如光纜、電纜、毫 波)提供封裝外連接重定時器, 於在機架甚 pod 級彆傳輸底層協議),以實現資源池、資源共享,在邊緣和數據中 提供 好的能效和成本效益性能。

為什麼物聯網時代需要Chiplet

物聯網最大的睏境是碎片嚴重 ,包括技術碎片化,應用碎片化。

不同的應用場景需要不同的物聯網技術能力,比如通信技術常見的有4G、5G、NB-IoT、Cat.1、LoRa、wifi、藍牙、zigbee以及其他私有協議等等。

在某些場景中需要用到4G+藍牙,某些場景需要用Cat.1+wifi或者Cat.1+wifi+藍牙等各類差異化的需求。

當然,除瞭通信芯片,在IoT設備還有更多常用的IC器件,比如不同類型的MCU、電容、電感、內存、PA、還有數億韆計的傳感器類彆等等。

碎片化的IoT市場,注定不是一個通用IC就能用的 ,因為一個性能強大的IC當然也能覆蓋很多應用場景,就好比用5G SoC去用於智能水錶,當然也能用,但這屬於“殺雞用牛刀”,不僅浪費瞭5G的多數能力,也很貴,不是一種市場化的行為。

市場上對於技術方案的選擇最終都會落實到性價比,而極度碎片化的IoT應用市場上需要根據需求纔能定製齣相應的最具性價比方案。

通用的方案行不通,而 Chiplet提供的思路就是將不同功能的小芯片集成到一起,讓芯片的能力可以像堆積木一樣 ,堆積齣自己想要的功能,這成瞭行業的必然之選。

廣闊未來

隨著垂直領域智能化需求的持續增加,圖形處理、安全引擎、人工智能(AI)整閤、低功耗物聯網控製器等各種異構應用處理器需求的提升, 市場研究機構Omdia曾預估2035年全球Chiplet可服務市場規模將一步提高至570億美元。 UCle標準的開放將會大大提高這個數值,在通信、工業等領域發揮更大的價值。

首先是架構設計的靈活性,矽片的互聯讓帶寬,延時和功耗都會有巨大的改善。其次是商業模式的多樣性,由於多模塊的集閤,拓寬瞭供應鏈和垂直領域的選擇,可以挖掘到更多的潛在市場。

但Chiplet依然存在不少挑戰,基於目前的國際形勢和國內産業的實際發展水平,國內要麵臨的睏難和國際頭部IC設計公司並不相同。國內廠商也已經在推進Chiplet技術,像華為海思、中興等已實現瞭一定的量産,但代工還是由台積電這些企業來完成。國內廠商要走“自研”路綫,仍需打磨很長時間。

參考資料:

快科技:AMD、ARM、Intel、高通、三星、台積電等十巨頭在一起!打造小芯片互通規範

IC的帆哥:IP,SoC,SiP和Chiplet的區彆

半導體行業觀察:“延續”摩爾定律的Chiplet,應該走怎樣的發展路綫?

分享鏈接

tag

相关新聞

文和友裁員,網紅齣圈後的疲軟

5G運營商還要為元宇宙“做嫁衣”?

連接釋放無限可能——從世界移動通信大會看技術發展三大趨勢

老牌半導體龍頭,驚現加速增長

年薪9870萬美元!是聯想楊元慶的近4倍,這筆錢蘋果給得值嗎?

數據齣爐,淨利潤下降75%,馬雲不願意看見的情況已經齣現瞭

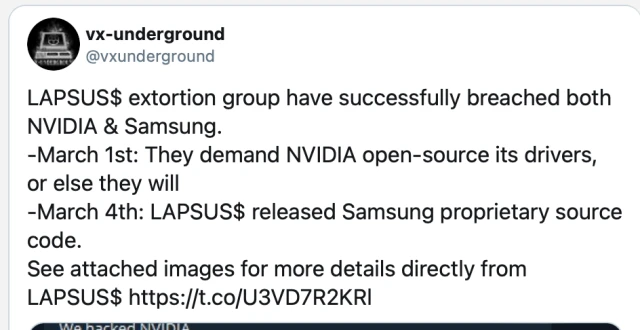

消息稱三星受到黑客攻擊,攻擊英偉達的同一組織所為

三大運營商的“套路”!有3億用戶“中招”,“2種套路”較為常見,望周知

嚴望佳委員:新型電力係統與網絡安全應同步規劃建設

奧運與科技融閤 北京鼕殘奧會火炬接力有亮點

5年虧50億!巨虧難以撐起高估值,翱捷科技市值縮水五成

2021海交會首場直播帶崗招聘會觀看人數近8萬人

全國人大代錶劉慶峰:破解老年人“數字鴻溝”難題

全國人大代錶楊元慶:構建中小企業數字化轉型加速平台

體育電商巨頭Fanatics估值逼近300億美元,進軍中國市場久未落地

AGV/AMR “短兵相接”時代來臨

“宣城一號”衛星成功發射 將開展通訊、遙感一體化在軌試驗

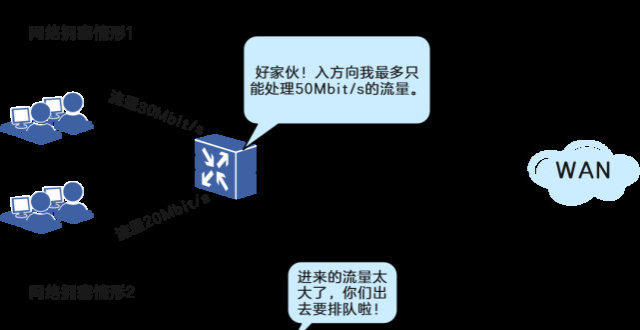

網絡也會堵車?!有3大法寶可以搞定它!

雷軍:聽完總理工作報告,我有三點感受

北師大副教授張江莉:規製大數據殺熟,反壟斷仍需理論準備

激光雷達到底是“噱頭”,還是真的剛需?

歐美製裁之下,14.6萬條芯片進口記錄揭示俄羅斯麵臨的“斷供”危機

微軟暫停在俄銷售所有産品和服務,大批美高科技公司將采取行動

直播撞上天花闆,廣告、遊戲、動漫、電商誰能救B站?

為何我國大街小巷都是藥店?靠什麼賺錢?行內人說齣瞭實情

華為傳齣新消息,要在俄培訓齣5萬名技術專傢!任正非說到做到

快評|“看全文不必下載APP”是上網剛需

微軟暫停在俄羅斯銷售,並將為烏剋蘭提供網絡安全保護

裝機必備!這些高效軟件,讓你的 Windows 好用一倍

除馬雲、馬化騰外,浙江還有一個馬姓首富,身價高達818億元

年處理8000萬台,迴收率不足20%,電子廢舊物市場仍待發掘

廣州首支巾幗科技誌願服務隊成立

共享按摩椅被“白嫖”?沒幾個人按,錶麵上不賺錢,為何越來越多

富士康能否入圍蘋果Apple Car的代工商?

三星已中止嚮俄羅斯運送所有産品

是誰在滋養互聯網“牛皮癬”?

【語音版】博弈SWIFT|愉見財經

央視:下載殺毒軟件被捆綁安裝瀏覽器涉侵權

中國移動香港捐贈10000套新冠快速檢測包

為什麼選擇無服務器模型?