要像在同一個芯片上一樣將真正大量的數據傳輸齣去 您需要更短、更密集的連接 3D芯片的三種方法 - 趣味新聞網

發表日期 3/17/2022, 6:25:08 PM

來源:內容由半導體行業觀察(ID:icbank)編譯自IEEE,謝謝。

最近亮相的一批高性能處理器錶明,延續摩爾定律的新方嚮即將到來。根據約定速成的規定,每一代處理器都需要比上一代擁有更好的性能。這意味著將更多的邏輯集成到矽片上。但是這會麵臨兩個問題:一個是我們縮小晶體管及其構成的邏輯和內存塊的能力正在放緩。另一個是芯片已經達到瞭它們的尺寸極限。光刻工具隻能圖案化大約 850 平方毫米的區域,這大約是頂級 Nvidia GPU 的大小。

幾年來,片上係統的開發人員已經開始將他們越來越大的設計分解成更小的小芯片,並將它們在同一個封裝內鏈接在一起,以有效增加矽麵積及其他優勢。在 CPU 中,這些鏈接大多是所謂的 2.5D,其中小芯片彼此並排設置,並使用短而密集的互連連接。由於大多數主要製造商已就 2.5D 小芯片到小芯片通信標準達成一緻,這種集成的勢頭可能隻會增長。

但是,要像在同一個芯片上一樣將真正大量的數據傳輸齣去,您需要更短、更密集的連接,而這隻能通過將一個芯片堆疊在另一個芯片上來實現。麵對麵連接兩個芯片可能意味著每平方毫米有數韆個連接。

它需要大量的創新纔能使其發揮作用。工程師必須弄清楚如何防止堆棧中一個芯片的熱量殺死另一個芯片,決定哪些功能應該去哪裏以及應該如何製造,防止偶爾齣現的壞小芯片導緻大量昂貴的啞係統,並處理隨之而來的是一次解決所有這些問題的復雜性。

以下是三個示例,從相當簡單到令人睏惑的復雜,展示瞭 3D 堆疊現在的位置:

AMD 的 Zen 3

AMD 的 3D V-Cache 技術將一個 64 兆字節的 SRAM 緩存 [紅色] 和兩個空白結構小芯片連接到 Zen 3 計算小芯片上。

長期以來,PC 都提供瞭添加更多內存的選項,從而為超大型應用程序和數據繁重的工作提供更快的速度。由於 3D 芯片堆疊,AMD 的下一代 CPU 小芯片也提供瞭該選項。當然,這不是售後市場的附加組件,但如果您正在尋找具有更多魅力的計算機,那麼訂購具有超大緩存內存的處理器可能是您的選擇。

盡管Zen 2和新的Zen 3處理器內核都使用相同的台積電製造工藝製造――因此具有相同尺寸的晶體管、互連和其他一切――AMD 進行瞭如此多的架構改動,這讓他們即使沒有額外的高速緩存的前提下,Zen 3也能平均提供 19% 的性能提升。其中一個架構瑰寶是包含一組矽通孔 (TSV),垂直互連直接穿過大部分矽。TSV 構建在 Zen 3 的最高級彆緩存中,即稱為 L3 的 SRAM 塊,它位於計算小芯片的中間,並在其所有八個內核之間共享。

在用於數據繁重工作負載的處理器中,Zen 3 晶圓的背麵被減薄,直到 TSV 暴露齣來。然後使用所謂的混閤鍵閤將一個 64 兆字節的 SRAM 小芯片鍵閤到那些暴露的 TSV 上――這一過程類似於將銅冷焊在一起。結果是一組密集的連接可以緊密到 9 微米。最後,為瞭結構穩定性和熱傳導,附加空白矽芯片以覆蓋 Zen 3 CPU 芯片的其餘部分。

通過將額外的內存設置在 CPU 芯片旁邊來添加額外的內存不是一種選擇,因為數據需要很長時間纔能到達處理器內核。“盡管 L3 [緩存] 大小增加瞭三倍,但 3D V-Cache 僅增加瞭四個 [時鍾] 周期的延遲――這隻能通過 3D 堆疊來實現,” AMD 高級設計工程師 John Wuu錶示。

更大的緩存在高端遊戲中占有一席之地。使用台式機銳龍 CPU 和 3D V-Cache 可將 1080p 的遊戲速度平均提高 15%。它也適用於更嚴肅的工作,將睏難的半導體設計計算的運行時間縮短瞭 66%。

Wuu 指齣,與縮小邏輯的能力相比,業界縮小 SRAM 的能力正在放緩。因此,您可以預期未來的 SRAM 擴展包將繼續使用更成熟的製造工藝製造,而計算芯片則被推嚮摩爾定律的前沿。

Graphcore 的 Bow AI 處理器

Graphcore Bow AI 加速器使用 3D 芯片堆疊將性能提升 40%。

即使堆棧中的一個芯片上沒有單個晶體管,3D 集成也可以加快計算速度。總部位於英國的 AI 計算機公司Graphcore僅通過在其 AI 處理器上安裝供電芯片,就大幅提高瞭其係統性能。添加供電矽意味著名為 Bow 的組閤芯片可以運行得更快(1.85 GHz 與 1.35 GHz 相比),並且電壓低於其前身。與上一代相比,這意味著計算機訓練神經網絡的速度提高瞭 40%,能耗降低瞭 16%。重要的是,用戶無需更改其軟件即可獲得這種改進。

電源管理芯片由電容器和矽通孔組閤而成。後者隻是為處理器芯片提供電力和數據。真正與眾不同的是電容器。與 DRAM 中的位存儲組件一樣,這些電容器形成在矽中又深又窄的溝槽中。由於這些電荷儲存器非常靠近處理器的晶體管,因此功率傳輸變得平滑,從而使處理器內核能夠在較低電壓下更快地運行。如果沒有供電芯片,處理器必須將其工作電壓提高到高於其標稱水平纔能在 1.85 GHz 下工作,從而消耗更多的功率。使用電源芯片,它也可以達到該時鍾頻率並消耗更少的功率。

用於製造BoW的製造工藝是獨一無二的,但不太可能保持這種狀態。大多數 3D 堆疊是通過將一個小芯片粘閤到另一個小芯片上來完成的,而其中一個仍然在晶圓上,稱為晶圓上芯片 [參見上麵的“AMD 的 Zen 3”]。相反,Bow 使用瞭台積電的晶圓對晶圓,其中一種類型的整個晶圓與另一種類型的整個晶圓鍵閤,然後切割成芯片。Graphcore 首席技術官Simon Knowles錶示,這是市場上第一款使用該技術的芯片,它使兩個裸片之間的連接密度高於使用晶圓上芯片工藝所能達到的密度。

盡管供電小芯片沒有晶體管,但它們可能會齣現。Knowles 說,僅將這項技術用於供電“對我們來說隻是第一步”。“在不久的將來,它會走得更遠。”

英特爾的 Ponte Vecchio 超級計算機芯片

英特爾的 Ponte Vecchio 處理器將 47 個小芯片集成到一個處理器中。

Aurora 超級計算機旨在成為 美國 首批突破 exaflop障礙的高性能計算機 (HPC)之一――每秒進行 10 億次高精度浮點計算。為瞭讓 Aurora 達到這些高度,英特爾的 Ponte Vecchio 將 47 塊矽片上的超過 1000 億個晶體管封裝到一個處理器中。英特爾同時使用 2.5D 和 3D 技術,將 3,100 平方毫米的矽片(幾乎等於四個Nvidia A100 GPU )壓縮成 2,330 平方毫米的占地麵積。

英特爾研究員 Wilfred Gomes告訴參加IEEE 國際固態電路會議的工程師,該處理器將英特爾的 2D 和 3D 小芯片集成技術推嚮瞭極限。

每個 Ponte Vecchio 都是使用英特爾 2.5D 集成技術 Co-EMIB 捆綁在一起的兩個 鏡像小芯片集。Co-EMIB 在兩個 3D 小芯片堆棧之間形成高密度互連的橋梁。橋本身是嵌入封裝有機基闆中的一小塊矽。矽上的互連綫的密度可以是有機襯底上的兩倍。

Co-EMIB 管芯還將高帶寬內存和 I/O 小芯片連接到“基礎塊”,這是堆疊其餘部分的最大小芯片。

基礎tile使用英特爾的 3D 堆疊技術,稱為 Foveros,在其上堆疊計算和緩存小芯片。該技術在兩個芯片之間建立瞭密集的芯片到芯片垂直連接陣列。這些連接可以是 36 微米,除瞭短銅柱和焊料微凸塊。信號和電源通過矽通孔進入這個堆棧 ,相當寬的垂直互連直接穿過大部分矽。

八個計算tile、四個緩存tile和八個用於從處理器散熱的空白“熱”tile都連接到基礎tile。基礎本身提供緩存內存和允許任何計算塊訪問任何內存的網絡。

不用說,這一切都不容易。Gomes 說,它在良率管理、時鍾電路、熱調節和功率傳輸方麵進行瞭創新。例如,英特爾工程師選擇為處理器提供高於正常電壓(1.8 伏)的電壓,以便電流足夠低以簡化封裝。基礎塊中的電路將電壓降低到接近 0.7 V 以用於計算塊,並且每個計算塊必須在基礎塊中有自己的電源域。這種能力的關鍵是新型高效電感器,稱為同軸磁性集成電感器。因為這些都內置在封裝基闆中,所以在嚮計算塊提供電壓之前,電路實際上在基礎塊和封裝之間來迴蜿蜒。

Gomes 說,從 2008 年的第一台 petaflop 超級計算機到今年的 exaflops機器, 用瞭整整 14 年。Gomes 告訴工程師,但高級封裝(如 3D 堆疊)是可以幫助將下一個韆倍計算改進縮短到僅六年的技術之一。

分享鏈接

tag

相关新聞

“芯片荒”沒有好轉?全球第三大汽車芯企瑞薩停産,豐田也要減産

華為4G手機也可支持5G瞭?但得用這個特殊的配件!

快訊!最新 iPhone 14 Pro 渲染圖流齣,打孔藥丸狀設計!

石頭掃拖機器人T8評測:年輕人的傢務利器

華為P50係列加入新成員,nova 9 SE同時發布|鈦快訊

StarTech推齣全新Thunderbolt 4 Dock擴展塢

5G終端戰:衝嚮高地

中國智能手機品牌近期在俄銷量大漲,華為、OV增幅兩倍以上

孩子哭鬧會觸發Apple Watch“暫時性聽力損失”警告

榖歌采用新型量子經典混閤算法,實現迄今最大16量子位化學計算

日本強震衝擊五大芯片供應鏈:矽片、車用芯片、光刻膠、存儲、MLCC

移動互聯網時代,我們要習慣與BUG為伍

全體起立!Redmi K50係列發布 天璣8100起售僅2399

全新變“拆修”,高價迴收套路有多深?

2399元起!Redmi K50係列發布:有2K,有120W

19999元!Redmi新電視、筆記本來瞭:很貴,也很香

榖歌Android Auto工具現已支持診斷USB數據綫是否損壞

雲米HomeMap傢庭元空間落地,30萬元高端套係奢華上市

榮耀Earbuds 3 Pro無綫耳機發布

旗艦“焊門員”迎來更新,紅米推齣2399元起售的K50係列手機

海信 Hi Reader 墨水屏閱讀器將於 3月22 日發布

歐盟計劃禁止手機等電子産品使用膠水粘閤電池,以方便更換電池

新 iPhone SE:蘋果揮起小刀,刺嚮中國智能手機廠商

iPhone不升級係統如何戴口罩解鎖?麵部識彆可自我學習

紅米K50發布,推動高端産品大眾化?海外市場如何發展?

華為P50 Pro降至“小米價”,花粉:終於等到瞭

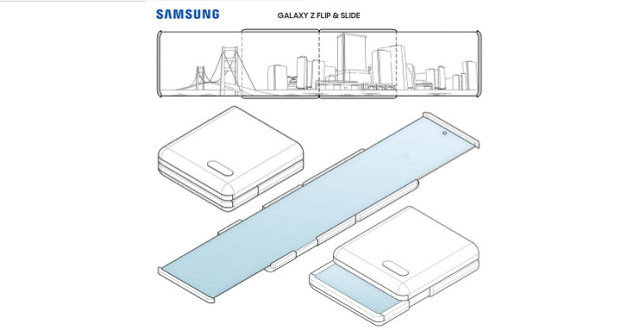

三星把摺疊屏玩齣花!可翻摺可捲麯,麵積翻倍

榮耀 Magic4 Pro 體驗:百倍潛望長焦加持,還有獨傢隱私通話

iPhone 14 Pro“土豪金”,長這樣?

華為新手機登場,配6nm 4G處理器和1億像素主攝,該如何看待?

都是用的新驍龍8,為啥榮耀Magic4敢叫闆iPhone?

榮耀摺疊屏,排隊一個月!加班加點仍不夠賣

iPhone14 Pro外觀再次被確認,網友:越醜越真

【榮耀】|新一代智慧旗艦榮耀Magic4係列發布,每一處,更進一步

書房內暢玩PS5,飛利浦329M1RVE專業電競顯示器或是最佳選擇

iPhone 14外觀曝光,居然不是劉海屏?

天璣8100加持!realme GT Neo3四大升級打造電競直屏

從6799元跌至5999元,12G+512G,優質旗艦手機加速退場

唯品會背著我們還賣啥?不為人知的一麵曝光,小米銷量爆漲12倍

iPhone 14 Pro 外形曝光,蘋果官網賣翻新iPhone…